# Proceedings of the 3<sup>rd</sup> International Conference on Applied Innovations in IT Eduard Siemens (editor in chief) et al.

# Proceedings of the 3<sup>rd</sup> International Conference on Applied Innovations in IT

Eduard Siemens (editor in chief) et al.

This volume contains publications of the 3rd International Conference on Applied Innovations in IT (ICAIIT), which took place in Koethen March 19th 2015. The conference is devoted to problems of applied research in the fields of automation and communications. The research results can be of interest for researchers and development engineers, who deal with theoretical base and the application of the knowledge in the respective areas.

Proceedings of the 3<sup>rd</sup> International Conference on Applied Innovations in IT, 2015.

editors: Prof. Dr. Eduard Siemens\* (editor in chief),

Dr. Bernd Krause\*, Dr. Leonid Mylnikov\*\*

(\*Anhalt University of Applied Sciences, \*\* Perm National Research Polytechnic University)

ISBN 978-3-86011-094-2 (Online)

### Content

| Section | 1. | Automation | and | algorithms |

|---------|----|------------|-----|------------|

|---------|----|------------|-----|------------|

| Anton Petrochenkov:                                                             |     |

|---------------------------------------------------------------------------------|-----|

| Practical Aspects of Genetic Algorithms Implementation for Life Cycle           |     |

| Management System of Electrotechnical Equipment                                 | 1   |

| Ivan Luzyanin, Anton Petrochenkov:                                              |     |

| Information Systems Dependability Analysis                                      | 7   |

| Leonid Mylnikov:                                                                |     |

| Conceptual Foundations of Modelling of Innovative Production Projects           |     |

| in Industrial Systems                                                           | 13  |

| Andrey Bachurin:                                                                |     |

| City Outdoor Lighting System Control. Problems and Prospects                    | 19  |

| Yuriy Babich:                                                                   |     |

| Long-term Forecasting of Frame Alignment Losses for Circuit                     |     |

| Emulation Implementation                                                        | .25 |

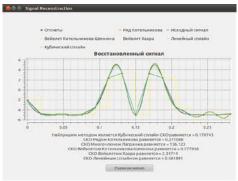

| Irina Strelkovskaya, Olena Lysiuk, Roman Zolotukhin:                            |     |

| Comparative Analysis of Signals Restoration by Different Kinds of Approximation | 29  |

| Section 2. Communication Technic                                                |     |

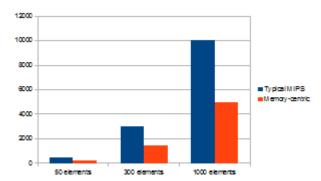

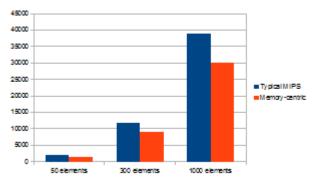

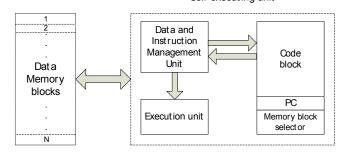

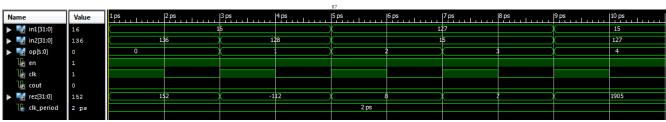

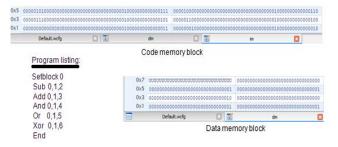

| Goce Dokoski, Danijela Efnusheva, Aristotel Tentov, Marija Kalendar:            |     |

| Software for Explicity Parallel Memory-Centric Processor Architecture           | 37  |

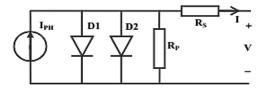

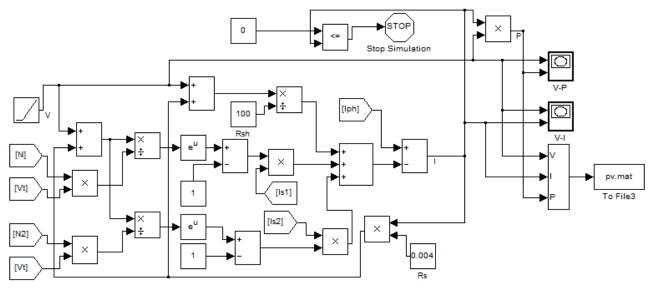

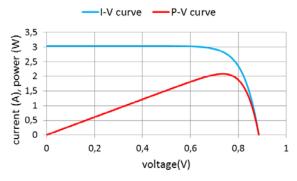

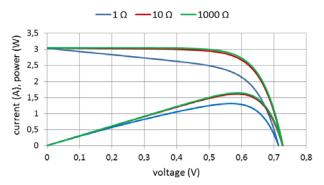

| Alena Okhorzina, Norbert Bernhard2, Alexey Yurchenko:                           |     |

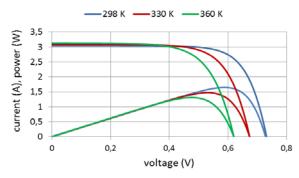

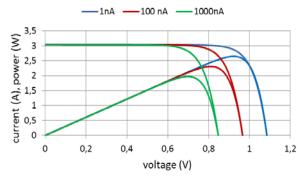

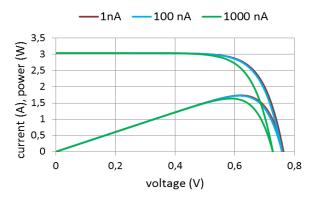

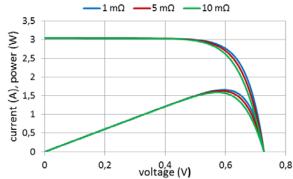

| Double-Exponential Model of PV with Temperature Depence                         | 41  |

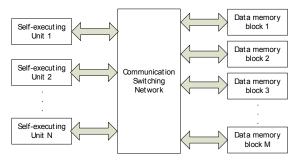

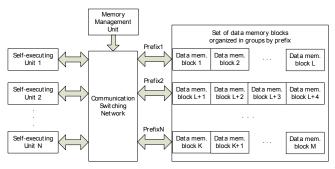

| Danijela Efnusheva, Goce Dokoski, Aristotel Tentov, Marija Kalendar:            |     |

| A Novel Memory-cenric Architecture and Organisation of Processors and Computers | 47  |

# Practical Aspects of Genetic Algorithms' Implementation in Life Cycle Management of Electrotechnical Equipment

Anton Petrochenkov Perm National Research Polytechnic University - Electrotechnical Department Komsomolsky Ave. 29, 614990, Perm, Russia

E-mail: pab@msa.pstu.ru

Abstract—Some practical aspects of Genetic algorithms' implementation regarding to life cycle management of electrotechnical equipment are considered.

Keywords: life cycle, electrotechnical equipment, genetic algorithms.

#### I. INTRODUCTION

The task of supporting an optimal conditions of electrotechnical equipment within the specified time is a key task. One of the main stages of the life cycle is the stage of maintenance, which acts as a stage of storage of statistical data, and as a stage of testing and inspection equipment to meet specified performance reliability.

One of the solution techniques, allowing creating effective algorithms for a wide range of tasks, is the usage of a subclass of the directed random search methods – methods of genetic modeling.

Numerous approbation of use and application of genetic methods in scientific and industrial spheres allow saying with confidence that when using the evolutionary methods, realization of the comprehensible well-founded decision search problems is always reached. In overwhelming majority of cases the use of natural analogues gives positive results. This is explained by the fact that the analogue taken from the nature was improved for many years of evolutions and at the present time has the optimum structure [1][2].

The idea is to consider these genetic algorithms regarding to life cycle management of electrotechnical equipment.

Like biological development each technological product develops continuously from a stage of origination (setting up) to a stage of collapse (recycling), going through any environment effects and adapting for them.

Algorithms work with a group of "individuals" – population, each of which represents possible solution of the given problem. Each individual is estimated by a measure of its "suitability" according to how rationally solution of the problem suits to it.

In each generation of the chromosome genetic algorithms (coded solutions) are the result of application of some genetic operations [1]-[3].

II. THE KEY GENETIC RELATIONS REGARDING LIFE CYCLE MANAGEMENT OF ELECTROTECHNICAL EQUIPMENT

Operations must precede the process of algorithms construction [1]-[3]:

- Selection of the initial conditions;

- Criteria selection (criteria functions);

- Analysis and selection of the boundary conditions.

Selection operations of the initial level depend on the type of the current task and goals, which must be reached as a result of algorithm realization.

If it concerns maintenance of the parameters on the certain level and reliability index of the equipment in the course of its operation then as initial conditions, it is reasonable to use data values of parameters and the indexes defined on a development stage in the form, installed by manufacturer and presented in the maintenance documentation (in particular, in maintenance documentation for the specific type of the equipment).

In this case, the main task is conformity «real reliability of the equipment – reliability set as zero conditions» that is support of higher level of reliability [4].

*Iinitial conditions* – datum values of the equipment parameters (values of reliability including the level of the serviceability, revitalization, mean time between failures, probability of non-failure operation etc.).

Population of candidate solutions  $P^{t}[3]$ :

$$P^t = \{P_1, P_2, \dots, P_{N_D}\},\$$

where

t = 0, 1, 2, ... is the number of generation;  $N_p$  is the population size. Chromosome consists of genes:

$$P_i = \{g_1, ..., g_L\},\$$

where L is the chromosome's length. Gene is identified by locus (position) and allele  $a_i$ :

$$g_j = \{j; a_j\}.$$

It is necessary to introduce criterion of an optimality estimation which will characterize level of considered

solutions under the control of the technical state of the equipment [3]-[6].

Realization of the genetic algorithm assumes the fitness function. This function returns the number, showing how good this chromosome is. The given function will be the criteria for the algorithm forming. In the embodied genetic algorithm it is reasonable at first to define the worse chromosome (having maximum deviations from the target level of parameter) and to measure the index value [3].

The got number is called the bad one with respect to which the quality of the other chromosomes is valued: fitness of the chromosome is calculated as difference between index value, set by the given chromosome and bad index value.

For chromosome  $P_1$  fitness function will be:

$$\omega(P_1) = |n - m|,\tag{1}$$

where

*n* is the current index (feature),

m is the specified index.

Let, for example, have a look some time resolution, limited by the first equipment failure. So as a criteria it is reasonable to use the index value of the mean time between failure of the given type of the electrotechnical equipment. The highest the value of the criterion function, the more optimal is the method of the equipment maintenance, the more optimal is the set of methods, providing this maintenance and their content (the set of the actions, the level and the quality of their realization).

The criteria choice is the main preliminary step when building the algorithm, because only it will define the further algorithm filling, its logical direction and convergence.

One of the important moments is the analysis and the limitation selection of the given system and for the algorithm is its functioning. Limitation can absolutely different indeed:

Economic ones – in the network of the limited founding:

Technological ones – limitation in the instrument base and documentation base, skilled personnel, etc.

Temporal constraints – conducting the actions, etc.

Limitations are the necessary addition, which lets to take into account the particularities of the real technological objects and systems, factors, influencing on its activity. The majority of the real tasks have deterministic character.

Limitations can be also made as some rules and conditions and can be used when selecting and making the possible variants of solutions (heuristics).

In this case, equipment is characterized by particular set of maintenances, with the help of which life cycle following is put into effect [7]. Each application for different methods can be done in different ways. This is the difference in chromosome genes.

This difference will be: in application of various instrument base (for example, in one case optical resources are used at a visual estimation of a state of pendant basic insulators, and in other – there is nothing), taking into account some external factors, in application to various approaches concerning state estimation (up to distance and

points control), and also in application to various methods of results processing.

It is necessary to add that all complex of actions should correspond to the circuit of support of the set technical state of the equipment (and to include not only actions for an estimation of the technical state in the form of monitoring and diagnostics, but also reducing and preventive operations etc.).

Changing of the purposes and the problems solved by system, can lead to revision as maintenances of preliminary operations, and a way of "filling" of chromosomes (for example, concerning economic aspect of a problem, the concepts connected with a given problematic and components can be used).

For the interpretation of genetic concepts, the following definitions are introduced [4].

Reproduction. It includes some elements of standardization, as the developed techniques of service and decision-making. As a result of a reproduction we will receive the element of electrotechnical equipment and a set of the regulated actions by means of which its support and the control of its technical state will be carried out.

Crossover. Refinement of existing techniques of the control and equipment service, on the basis of expert estimations and other sorts of the analysis of existing systems. Framing of concrete solutions on upgrading, support of any solutions of documentation base is necessary. The completion phase is development of the standard of the enterprise regulating and considering all features of a set of actions under the control and support of the set technical state of the equipment.

There are a lot of crossover techniques [3]. Indeed the structure of crossover affects the efficiency of genetic algorithm.

Let's introduce three main crossover techniques, which will later be used in the construction of algorithms for optimal life cycle management system of electrotechnical equipment.

1) One-point crossover.

Let's have 2 chromosomes  $P_1$  and  $P_2$  in population P:  $P_1 \in P$ ,  $P_2 \in P$ , which will be choose as parents:

$$P_1 = \{g_1, g_2, ..., g_L\},\$$

$P_2 = \{g^1, g^2, ..., g^L\}.$

It is necessary to determine the cut-point of crossover k- this point determines the place of two chromosomes, where they should be "cut", i.e. k is the number (or value) of the code of a gene which is performed after incision chromosome:

$$k \in \{1, 2, \dots, L-1\}.$$

In this case there will be two new chromosomes  $P'_1$  and  $P'_2$  formed by permutations of the elements in chromosomes  $P_1$  and  $P_2$  according to the rule:

$$P'_{1} = \{g_{1}, g_{2}, g_{k}, | g^{k+1}, ..., g^{L} \},$$

$$P'_{2} = \{g^{1}, g^{2}, g^{k}, | g_{k+1}, ..., g_{L} \}.$$

Schematically one-point crossover provides convertion two chromosomes and partial exchange of information between them.

#### 2) N-point crossover.

Unlike one-point crossover, it is necessary to determine the N cut-points in each of  $P_1$  and  $P_2$  chromosomes. Cut-points divide the chromosome into several blocks, and chromosomes exchange sites located within blocks. E.g., the offspring  $P_1'$  is formed from the odd blocks of parent  $P_1$  and even blocks of parent  $P_2$ . The offspring  $P_2'$  is formed from the odd blocks of parent  $P_2$  and even blocks of parent  $P_1$  respectively:

$$P_{1} = \{g_{1}, ..., g_{a}, | g_{a+1}, ..., g_{i}, | g_{i+1}, ..., g_{k}, | g_{k+1}, ..., g_{L}\}$$

$$P_{2} = \{g^{1}, ..., g^{a}, | g^{a+1}, ..., g^{i}, | g^{i+1}, ..., g^{k}, | g^{k+1}, ..., g^{L}\}$$

$$P'_{1} = \{g_{1}, ..., g_{a}, | g^{a+1}, ..., g^{i}, | g_{i+1}, ..., g_{k}, | g^{k+1}, ..., g^{L}\}$$

$$P'_{2} = \{g^{1}, ..., g^{a}, | g_{a+1}, ..., g_{i}, | g^{i+1}, ..., g^{k}, | g_{k+1}, ..., g_{L}\}$$

However, it is necessary to take into account that a large number of cut points may result in loss of "good" parents properties.

#### 3) "Cut and splice".

"Cut and splice" crossover is used by forming the second and further generation.

In this approach, the blocks are analyzed in both chromosomes and partial correspondence between the elements of the first and second parents with forming offsprings is set. In the portable block the duplicate genes (alleles) are replaced by genes (alleles) presented in the locus of original chromosome:

$$P_{1} = \{g_{1}, g_{2}, ..., |g_{i}^{i}|, |g_{k}, g_{k+1}, ..., g_{L}\},\$$

$$P_{2} = \{g^{1}, g^{2}, ..., ..., |g^{k}|, |g_{i}^{i}|, ..., g^{L}\},\$$

$$P'_{1} = \{g_{1}, g_{2}, ..., |g_{i}^{i}|, |g^{k}|, |g_{k+1}|, ..., g^{L}\},\$$

where

$g_i^i$  is duplicate gene in chromosomes  $P_1$  and  $P_2$ :

$$g_i^i := \{i, a_{k+1}\}.$$

*Mutation.* In whole, a mutation is the ambiguous phenomenon in most cases calling negative consequences. In this case under mutation we will understand effect of some factors on equipment maintenance. To mutation factors we refer:

- Environment conditions (the external factor, in view of object distribution is important);

- Skills degree of operating staff.

Let's introduce two main mutation techniques, which will later be used in the construction of algorithms for optimal life cycle management system of electrotechnical equipment.

#### 1) One-point mutation.

In the chromosome  $P_1$ ,  $P_1 \in P$ , it's need to determine (randomly or specifically) the two positions (two loci) (i) and (L-i):

$$P_1 = \{g_1, g_2, ..., g_i, ..., g_{L-i}, ..., g_L\}.$$

Genes corresponding to selected positions,  $g_i$  and  $g_{L-i}$ , are rearranged. It caused to form a new chromosome:

$$P'_{1} = \{g_{1}, g_{2}, ..., g_{L-i}, ..., g_{i}, ..., g_{L}\}.$$

#### 2) N-point mutation.

It's necessary to determine the N cut-points in the chromosome  $P_1, P_1 \in P$ .

After that step by step the genes located to the right of the cut-points are exchange of each other in order of their location. The gene located to the right of the last cut-point goes into position in front of the gene corresponding to the first cut-point:

$$P_1 = \{g_1, ..., g_a, |g_{a+1}, ..., g_i, |g_{i+1}, ..., g_k, |g_{k+1}, ..., g_L\}$$

$$P'_1 = \{g_1, ..., g_a, |g_{k+1}, ..., g_i, |g_{a+1}, ..., g_k, |g_{i+1}, ..., g_L\}$$

*Inversion*. Inversion is a mathematical construction that allows the inversion based on parent chromosome (or part thereof) to create a offspring chromosome.

Let's introduce two main inversion techniques, which will later be used in the construction of algorithms for optimal life cycle management system of electrotechnical equipment.

#### 1) One-point inversion.

It's necessary to determine the cut-point of inversion k in the chromosome  $P_1, P_1 \in P$ :

$$k \in \{0,1,2,\ldots,L+1\}.$$

Offspring  $P'_1$  is formed by inversion of the segment located to the right of cut-point k in the chromosome  $P_1$ :

$$\frac{P_1 = \{g_1, g_2, g_k, | g_{k+1}, \dots, g_L\}}{P_1' = \{g_1, g_2, g_k, | g_L, \dots, g_{k+1}\}},$$

#### 2) N-point inversion.

It's necessary to determine the N cut-points in the chromosome  $P_1$ ,  $P_1 \in P$ . Then elements formed inside the blocks are inverted:

$$P_1 = \{g_1, ..., g_a, |g_{a+1}, ..., g_i, |g_{i+1}, ..., g_k, |g_{k+1}, ..., g_L\}$$

$P_1' = \{g_1, ..., g_a, | g_i, ..., g_{a+1}, | g_{i+1}, ..., g_k, | g_L, ..., g_{k+1}\}$  Reduction. Reduction is a mathematical construction (based on the analysis of the population) that allows to reduce the size of the population to a predetermined value after one or more generations of genetic algorithm.

The primary purpose of the reduction is eliminating unsuccessful decisions and maintaining population at an optimal level (depending on computer memory).

Reduction carried out the following procedures:

- 1) the forming a reproduction group from all the solutions generated in the population  $P^t$ ,

- 2) the selection of solutions in the following population. Size of new population  $N^{t+1}$  is defined as:

$N^{t+1} = N^t + N_{\text{OC}} + N_{\text{OM}} + N_{\text{OI}},$

where

$N^{t}$  is the size of population on step before (t),  $N_{OC}$  is the

number of offsprings produced by crossover,

$N_{\rm OM}$  is the number of offsprings produced by mutation,  $N_{\rm OI}$  is the number of offsprings produced by inversion.

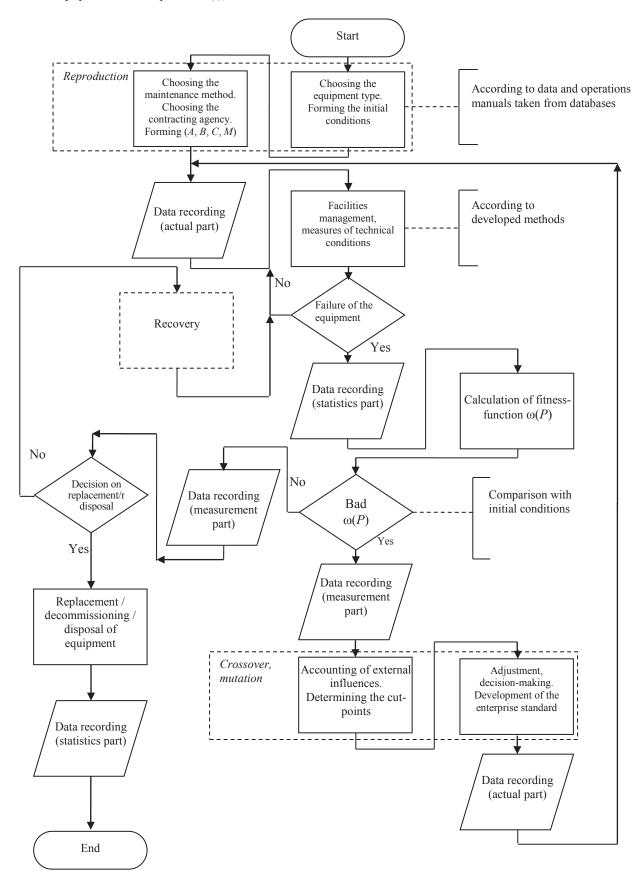

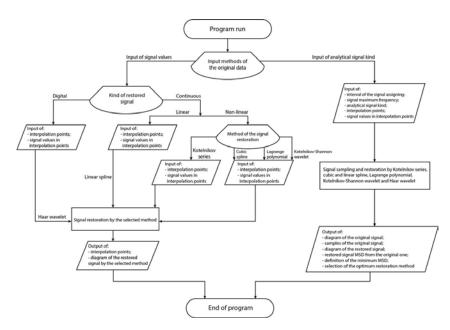

Fig. 1. Generic flowchart of life cycle management system of electrotechnical equipment with the use of genetic algorithms.

# III. IMPLEMENTATION OF GENETIC ALGORITHMS IN THE TASK OF SUPPORTING AN OPTIMAL CONDITIONS OF ELECTROTECHNICAL EQUIPMENT

Generic flowchart of life cycle management system of electrotechnical equipment with the use of genetic algorithms is showed in the Fig. 1. From the figure it can be seen that the performance of each group of measures to support the optimal conditions affects the function of the life cycle equipment as a whole [8]-[11].

The reliability plan also includes a detailed description of reliability tools and criteria for critical items list [7]. As the function of reliability, the function of the life cycle equipment R'(t) should provide maximum effort to specified conditions, i.e., the effective maintenance model should ensure the maintenance of the set of indicators at the appropriate level:

$$R'(t) = R_0 - (A(p) + B(p) + C(p) + M(p) + ...) \le 0,$$

where  $R_0$  is the specified reliability, A(p), B(p), C(p), M(p) are the "parts" of reliability, provides a variety of measures [9][10][12].  $A = \{a_1, a_2, a_3\}$  is a variety of information-obtain-actions,

$a_1$  – monitoring by «hectic rush»,  $a_2$  – monitoring, based on the visual examination of the equipment,  $a_3$  – monitoring with the use of infrared and ultraviolet control,

$B = \{b_1, b_2, b_3\}$  is a variety of rules of estimation of technical conditions,  $b_1$  – analysis based on risk model,  $b_2$  – analysis based on probabilistic assessment of failures,  $b_3$  – analysis based on expert judgment,

$C = \{c_1, c_2, c_3\}$  is a variety of maintenance and repair activities,  $c_1$  — maintenance by «hectic rush»,  $c_2$  — preventative maintenance,  $c_3$  — maintenance within a system of service within a given technical condition,

$M = \{m_1, m_2, m_3\}$  is a variety of management methods.

Let's introduce the next basic heuristics:

$$H_1 = \{a_1c_1\},\$$

$H_2 = \{a_2c_2\},\$

$H_3 = \{a_3c_3\}.$

Each group of measures provides a certain level of selected indicators, the value of which varies from 1 to 10. The initial conditions are based on the available basic parameters of reliability of different types of electrotechnical equipment.

Let's assume that each of the groups of measures has the same weight in forming the reliability in current time. Thus the maximum value (A(p) + B(p) + C(p) + M(p) + ...) is equal to 40.

In case of absolute terms (e.g. time between failure  $t_{\text{max}}$ ) it can be used the calibration scale groups of measures of reliability indices of a particular type of equipment:

- $t_{\text{max}}$  corresponds to 40 relative units,

- calculating the calibration factor  $k_{\kappa} = \frac{t_{\text{max}}}{40}$ ,

- the computational procedures returns to the operator the value of the function of the life cycle equipment in absolute terms  $(a_n + b_n + c_n + m_n) \cdot k_{\kappa}$ .

E.g., to suspension insulators PS-70 with  $t_{\text{max}} = 360$  months, the calibration factor is  $k_K = 9$  and the equation of the function of the life cycle equipment takes the form:

$$a_n + b_n + c_n + m_n \ge 40,$$

(2)

where

n = 1...3 is the name of heuristic.

The first generation of chromosomes is formed basing on the evaluation of a particular type of electrotechnical equipment in four different power systems (Table 1).

TABLE I GENERATION OF NEW POPULATION

| Chromosome | (a,b,c,m)    |

|------------|--------------|

| $P_1$      | (5, 5, 8, 7) |

| $P_2$      | (2, 5, 4, 3) |

| $P_3$      | (5, 4, 4, 3) |

| $P_4$      | (8, 4, 7, 7) |

To calculate the coefficients of fitness  $\omega(P_i)$ , it's necessary to substitute each solution in (2) and find the deviation from the formula (1) (Table 2).

TABLE II

CALCULATION OF THE FITNESS-FUNCTION

| CRECCERTION OF THE TITALESS FOR CHOIN |             |  |  |  |  |  |  |

|---------------------------------------|-------------|--|--|--|--|--|--|

| Chromosome                            | $\omega(P)$ |  |  |  |  |  |  |

| $P_1$                                 | 40-25=15    |  |  |  |  |  |  |

| $P_2$                                 | 40-14=26    |  |  |  |  |  |  |

| $P_3$                                 | 40-16=24    |  |  |  |  |  |  |

| $P_4$                                 | 40-26=14    |  |  |  |  |  |  |

The higher fitness (less the value of  $\omega_i(P)$ ), the greater the chance of being selected as a parent chromosome (Table 3).

TABLE III

SELECTION OF PARENT CHROMOSOMES

| 1st parent chromosome | 2 <sup>nd</sup> parent chromosome |

|-----------------------|-----------------------------------|

| P <sub>4</sub>        | P <sub>1</sub>                    |

| $P_4$                 | P <sub>3</sub>                    |

| $P_4$                 | $P_2$                             |

| $P_1$                 | $P_3$                             |

| $P_1$                 | $P_2$                             |

| $P_3$                 | $P_2$                             |

Let's use the crossover for generation the offspring chromosome (Table 4). The result is a second generation of chromosomes with their usual fitness (Table 5).

TABLE IV CROSSOVER

| 1 <sup>st</sup> parent<br>chromosome | 2 <sup>nd</sup> parent<br>chromosome | Offspring chromosome |

|--------------------------------------|--------------------------------------|----------------------|

| (8  4, 7, 7)                         | (5  5, 8, 7)                         | (8, 5, 8, 7)         |

| (8  4, 7, 7)                         | (5 4,4,3)                            | (8, 4, 4, 3)         |

| (8  4, 7, 7)                         | (2 5,4,3)                            | (8, 5, 4, 3)         |

| (5  5, 8, 7)                         | (5 4,4,3)                            | (5, 4, 4, 3)         |

| (5 5,8,7)                            | (2 5,4,3)                            | (5, 5, 4, 3)         |

| (5 4,4,3)                            | (2 5,4,3)                            | (5, 5, 4, 3)         |

TABLE V Offsping's Fitness

| Offspring chromosome | $\omega(P)$ |

|----------------------|-------------|

| (8, 5, 8, 7)         | 40-28=12    |

| (8, 4, 4, 3)         | 40-19=21    |

| (8, 5, 4, 3)         | 40-20=20    |

| (5, 4, 4, 3)         | 40-16=24    |

| (5, 5, 4, 3)         | 40-17=23    |

| (5, 5, 4, 3)         | 40-17=23    |

Continuing in this way, one chromosome eventually reaches fitness, equal to 0 or close to it.

#### IV. CONCLUSION

It is also necessary to take into account additional "financial" criterion, calculating the additional factors of fitness. Thus, the choice of the optimal solution will be a synthesis of solutions for two functions: the function of "reliability" and function of "costs" [3][13].

The difficulty and the goodness of action realizations in technical state of the equipment increases, the number of the operations required for the algorithm realization increases. But in spite of the apparent bulking, algorithms are simple in their accomplishment because of their coherency.

Electronic educational resources were developed using an educational process for training students with the specializations "Electrical Power Supply," "Automation of Technological Processes and Production," and "Automated Management of Product Life Cycle" of Perm National Research Polytechnic University.

Works on this direction are conducted within the Russian Foundation for Basic Research Grant of Russia No 14-07-96000 "Development of an intellectual decision support system to ensure of energy facilities trouble-free operation".

#### REFERENCES

- L. A. Gladkov, V. V. Kurejchik, V. M. Kurejchik, "Genetic algorithms", Under the editorship of V.M. Kurejchik. – M: FIZMATLIT, 2006. (rus)

- [2] D. E. Goldberg, "Genetic Algorithms in Search, Optimization and Machine Learning", Addison-Wesley, 1989.

- [3] H. Aytug, M. Khouja and F. E. Vergara, "Use of genetic algorithms to solve production and operations management problems: A review", International Journal of Production Research, 2003, 41:17, pp.3955-4009, doi: 10.1080/00207540310001626319

- [4] A. Petrochenkov, "Regarding to Implementation of Genetic Algorithms in Life Cycle Management of Electrotechnical Equipment", Proc. of the Second International Conference on Applied Innovations in IT, E. Siemens (editor in chief) et al. Kothen, Anhalt University of Applied Sciences, 2014. – pp. 79-83. doi: 10.13142/kt10002.13.

- [5] D. Garg, K. Kumar and Meenu, "Availability Optimization for Screw Plant Based on Genetic Algorithm," International Journal of Engineering Science and Technology, vol. 2, No. 4, pp 658-668, 2010

- [6] S.P. Sharma, Y.Vishwakarma, "Availability optimization of refining system of Sugar Industry by Markov process and Genetic Algorithm", Proc. of the 2014 International Conference on Reliability, Optimization and Information Technology, art. no. 6798290, pp. 29-33. doi: 10.1109/ICROIT.2014.6798290

- [7] E.V. Cota, L. Gullo, R. Mujal, "Applying Design for Reliability to increase reliability confidence", Proc. of Annual Reliability and Maintainability Symposium, 2014, art. no. 6798454, doi: 10.1109/RAMS.2014.6798454

- [8] A. Petrochenkov, "Methodical Bases of the Integrated Electrotechnical Complexes Life Cycle Logistic Support", Proc. of the First International Conference on Applied Innovations in IT, E. Siemens (editor in chief) et al. Dessau, Anhalt University of Applied Sciences, 2013. – P.7-11. doi: 10.13142/kt10001.02.

- [9] A. B. Petrochenkov, "Regarding Life-Cycle Management of Electrotechnical Complexes in Oil Production", Russian Electrical Engineering, 2012, vol. 83, No.11, pp.621-627. doi: 10.3103/S1068371212110090.

- [10] A. B. Petrochenkov, "On the Problem of Development of Models of Processing Operations Performed during Repair of Electrical Engineering Complex Components", Russian Electrical Engineering, 2013, Vol. 84, No. 11, pp. 613–616. doi: 10.3103/S1068371213110096.

- [11] A. B. Petrochenkov, S. V. Bochkarev, A. V. Romodin, D. K. Eltyshev, "The Planning Operation Process of Electrotechnical Equipment Using the Markov Process", Russian Electrical Engineering, 2011, Vol. 82, No.11., pp.592-595. doi: 10.3103/S1068371211110113.

- [12] N.A.J. Hastings, "Physical Asset Management", 2015. doi: 10.1007/978-3-319-14777-2 3

- [13] A. B. Petrochenkov, A. V. Romodin, "Energy-optimizer complex", Russian Electrical Engineering, 2010, vol. 81, no. 6, pp. 323-327. doi: 10.3103/S106837121006009X.

# Regarding Information Systems Dependability Analysis

Ivan Luzyanin, Anton Petrochenkov Perm National Research Polytechnic University - Electrotechnical Department Komsomolsky Ave. 29, 614990, Perm, Russia

E-mail: {lis, pab}@msa.pstu.ru

Abstract—The article presents classification of information systems by different parameters. Factors influencing information systems dependability are also presented. The article describes the strategy of information systems dependability analysis and methods of its increase. The example of analysis of real information system is considered to show how to implement the strategy.

*Keywords*: information system, dependability, maintainability, reparability, integrated logistics support, structural and functional analysis.

#### I. INTRODUCTION

Nowadays information systems perform different tasks almost in all fields of human activity. Their responsibility increase rapidly for the last time. For that reason, providing the information systems dependability becomes more and more important.

The aims of research are the information systems dependability estimation criteria determination and dependability increasing methods development.

We consider the information system as a hardware system. The software of this system is considered as the component, which provides working of the system, and delivers a human-machine interface. The special attention is paid to hardware dependability.

In this report, we will consider information systems as a whole and highlight their features. We will also describe the generic algorithm of information systems dependability analysis and give the methods of dependability increase.

As a main dependability definition, we use the definition given in the standards IEC 60050-191:1990 [1] and IEC 60300-3-1:2003 [2].

In this term, availability performance is the ability of an item to be in a state to perform a required function under given conditions at a given instant of time or over a given time interval, assuming that the required external resources are provided.

Reliability performance is the ability of an item to perform a required function under given conditions for a given time interval.

Maintainability performance is the ability of an item under given conditions of use, to be retired in, or restored to, a state in which it can perform a required function when maintenance is performed under given conditions and using stated procedures and resources.

Maintenance support performance is the ability of a maintenance organization, under given conditions, to provide upon demand, the resources required to maintain an item, under a given maintenance policy.

The given conditions in these definitions are related to the item itself and to the conditions under which the item is used and maintained.

#### II. OBJECT ANALYSIS

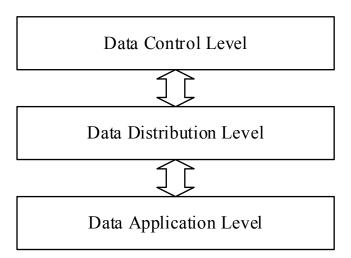

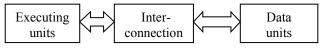

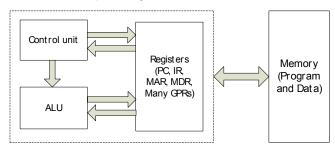

The generic structure of the information system can be presented as a three-level model (Fig. 1).

Fig. 1. Information systems generic structure

Upper level is responsible for working of IT-infrastructure. The centralized data processing, general-system services delivering, data storage and shared resources control are performed here. This level also provides data integrity and safety.

Middle level provides safe data transmission, data integrity control during the transmission and data routing.

Lower level provides client workstations and peripherals working.

Every level has a specific structure and performs different tasks; therefore, it is necessary to study working of these levels separately.

Moreover, every real implementation of the information system has specific parameters. Every specific parameter needs additional studying.

It is impossible to describe all variants of information systems implementation. So that, let's try to classify these

implementations according to different parameters. After that one can present the most common specifics and regularities of real information systems in each class.

The information systems can be classified by following parameters:

- a) On geographical distribution:

- Distributed systems;

- Centralized systems.

- b) On performed tasks:

- Corporate Networks;

- Data processing centers.

- Information systems of network providers.

- c) On application field:

- Industrial information systems;

- Administrative Information systems;

- Information systems included both industrial and administrative levels.

Distributed information systems are located in several buildings. The system consists of several segments. This type of systems usually has central segment placed in the main building and a number of local segments, which are able to work independently from each other. Central segment equipment delivers general services such as connection between segments, providing access to the Internet and others. If the central segment equipment fails, other segments are not able to use general services but are still able to perform local operations. The most critical levels in these systems are central data control level and central data distribution level. Its dependability must be higher than dependability of other ones. The failures of central data application level may not cause general functions failures and do not affect working of other segments but in this case central layer administrators may lose control of the system. Therefore, its dependability has to be higher as well.

The structure of centralized information system can be presented as one local segment of distributed information system.

The purpose of corporate networks is to support users working. Hence, the tasks of data application level determine the structure and functions of these systems. This layer is usually the largest one in this system.

The data processing centers are high-performance systems, which perform complex operations with the large amount of data. The tasks of data control level determine its structure and functions.

The data distribution level can be conventionally divided into internal (which provides communication between data center servers) and external (which connects the data center and external users) levels.

In these centers, it may be no data application level for example if the data center performs the cloud computing.

The main task of the information systems of network providers is to provide data transmission. There is no data application level in this type of information systems. Its structure and functions are defined by the data distribution level, and the task of data control level is to distribute information between clients according to their requests.

The industrial information systems are usually real-time systems. They provide working of automated control systems. These systems deliver the human-machine

interface and allow controlling real state of the technological process. They are critical systems. Their failures may cause massive destruction or any more critical aftermaths. So that, these systems must have high dependability and long lifetime

The administrative information systems are not real-time systems. These systems support office working and their failures are not so critical as industrial information systems failures. The faults of them may cause economic loses but usually not affect human health and life and not cause massive destruction. Therefore, the dependability of these systems depends on aftermath scale caused by their failures.

## III. INFORMATION SYSTEMS DEPENDABILITY FACTORS ANALYZING

After information systems analyzing let's study the factors influencing information systems dependability.

These factors are divided into internal and external ones.

- 1) The internal factors are:

- Elements dependability;

- Amount of elements;

- Elements joining method.

- 2) The external factors are:

- Environmental conditions;

- Usage strategy (including usage time and intensity, user's qualification, work organization);

- System structure;

- Software used.

The internal factors affect working of information system equipment and the external factors affect working of information system as a whole.

The analysis of studies in the field of microelectronics and computing equipment dependability [3]-[7] showed that there are quite different methods of eliminating every concrete factor. The analysis of different examples of real information systems implementations [8][9] provides distinguish three basic groups of arrangements used to eliminate influence of described factors:

- 1) Technological arrangements that increase the system dependability using the maintenance and repair policy.

- 2) Organization arrangements, that allow increasing dependability by changing usage strategy (e.g. by optimizing usage time and intensity or employing more qualified specialists).

- 3) Arrangements on structure optimization, that increase dependability due to changing of system structure.

On this step, the problem of arrangement choosing is faced. It is also necessary to have to develop the concrete methods of implementing these arrangements in real information systems.

To solving these problems the strategy of information systems dependability analysis and methods of its increase are developed. If data are to be reliable, the instrumentation used has to be reliable too [10].

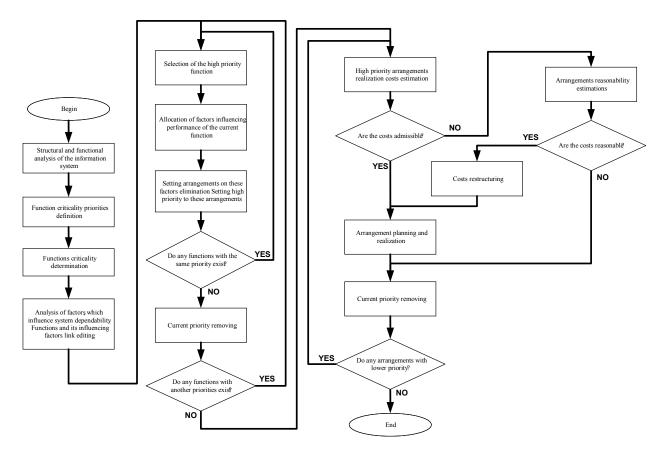

The algorithm has iterative structure. The amount of iterations depends on amount of functions and priorities. This algorithm is the implementation of the integrated logistics support (ILS) methodic for information systems.

The first part of this algorithm corresponds to the Failure Modes, Effects and Criticality Analysis (FMECA) procedure [11]. (Fig. 2).

Using the accumulated statistics corresponding to the separate junctions of a system, each type of the system component can be related to a definite law of failure intensity, assuming the latter to be a constant value at minimum statistics. The influence of external unfavorable factors on the system in this case cannot be determined; thus, the distribution law and its parameters cannot be correctly obtained either. Use of the guide data corresponding to the analogs of the system components may be a way out of this situation. Knowledge of the dependability component does not provide information concerning the dependability of the system as a whole. For analyzing the system one should know its structure and inner functional connections. In structural design, the dependability of a structural component is evaluated with respect to one or more failure modes. There are a lot of methods for constructing failure models of complex systems [12]. One of the approaches for models under incomplete information based on the set of canonical analytical expressions for computing imprecise structural reliability has been obtained by Lev V.Utkin, and Igor O.Kozine [13].

The second part implements the reliability centered maintenance including condition based monitoring procedure [11]. The latter task entails selection of the

servicing system, development of control and diagnostics systems, processing and analysis the data for obtaining information on performance quality, carrying out various stages of maintenance according to technical and economy criteria, and increasing the quality of reconstruction [14]-[17].

The third part defines the profitability of arrangements to be determined [2][5][14]. The arrangements planning and implementation are also performed in this part.

One can use this algorithm in case of a small enterprise budget and having problems with working of IT-infrastructure. It may be problems with a low data transmission time in the network or frequent failures of the network equipment. So, this is the most general algorithm.

There is the task of implementing this algorithm for solving real systems problems. For this purpose, it is necessary to describe formally all procedures of this algorithm as applied to information systems.

It is also need to develop concrete realization methods of these algorithm positions, which allow solving real problems.

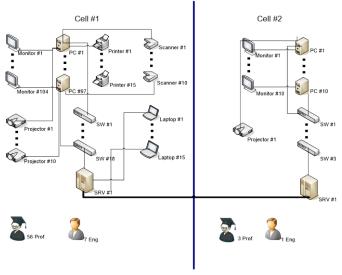

Let's describe only the structural and functional analysis methods for information systems. Let's consider these methods on the example of the Microprocessor Units of Automation chair infrastructure in the Perm National Research Polytechnic University. The hardware structure of this system is shown on Fig. 3.

Fig. 2. The strategy of information systems analysis and their dependability increasing methods choosing

Fig. 3. The IT-infrastructure of the Microprocessor Units of Automation chair in Perm National Research Polytechnic University

The system consists of two segments. The main segment supports working environment for fifty six professors. Seven engineers provide technical support, maintenance and repair of the system. The second segment supports working environment for three professors and maintained by one engineer.

The detailed structure of this information system is shown on Fig. 4.

The PCs and servers are detailed into their internal replaceable modules but network equipment and peripherals are detailed into concrete devices due to repairing them in service centers.

Fig. 4. Information system detailed structure

The functional structure of the information systems is determined by its software. The basic software used in the chair's information systemis shown on the Fig. 5.

Fig. 5. Software used on the chair's information system

On the described system, there are organization problems on all levels. For example: there are no technical descriptions and schemes of this system, there are no concrete usage rules, which makes impossible to support this system. There also structural problems (the network structure do not provide stable interconnection between equipment). There are some technological problems because of some equipment is very old.

#### IV. CONCLUSION

This example illustrated the implementation of the first part of the algorithm described previously. In future, we plan to develop implementation methods for all steps of the algorithm. The experimental analysis of our chair information system using this algorithm will be carried out. It is also necessary to generalize the described strategy on all information systems classes. The task is to find concrete enterprises with different types of information systems to conduct more experiments and test this strategy in real conditions.

Works on this direction are conducted within the Russian Foundation for Basic Research Grant of Russia No 14-07-96000 "Development of an intellectual decision support system to ensure of energy facilities trouble-free operation".

#### REFERENCES

- [1] IEC 60050-191:1990 International Electrotechnical Vocabulary. Chapter 191: Dependability and Quality of Service.

- [2] IEC 60300-3-1:2003 "Dependability management Part 3-1: Application guide - Analysis techniques for dependability - Guide on methodology".

- [3] R. Longbottom "Computer System Reliability", New York: Wiley-Blackwell, 1980.

- [4] P. Gill, N. Jain, N. Nagappan, "Understanding Network Failures in Data Centers: Measurement, Analysis and Implementations" Microsoft Research, Redmond WA.

- [5] B. Guenter, N. Jain, C. Williams, "Managing Cost, Performance, and Reliability Tradeoffs for Energy-Aware Server Provisioning", Microsoft Research, Redmond WA.

- [6] J. Gray, "Why Do Computers Stop and What Can Be Done About It?", 1985.

- [7] S.C. Malik, "Reliability modeling of a computer system with preventive maintenance and priority subject to maximum operation and repair times", International Journal of System Assurance Engineering and Management, vol. 4, no. 1, pp. 94-100, Mar. 2013.

- [8] R. Reinertsen, "Residual life of technical systems; diagnosis, prediction and life extension", Reliability Engineering and System Safety, 1996, 54 (1), pp. 23-34. doi: 10.1016/S0951-8320(96)00092-0

- [9] A.K.S. Jardine, D. Lin, and D. Banjevic, "A review on machinery diagnostics and prognostics implementing condition-based maintenance", Mechanical Systems and Signal Processing, 2006, 20 (7), pp. 1483-1510. doi: 10.1016/j.ymssp.2005.09.012.

- [10] M. Bagajewicz, "A review of techniques for instrumentation design and upgrade in process plants", Canadian Journal of Chemical Engineering, 2002, 80 (1), pp. 3-16.

- [11] JSP 886 The Defence Logistic Support Chain Manual vol. 7 Integrated Logistics Support

- [12] A. B. Petrochenkov, E. M. Solodkii, "On the Methods for Constructing Failure Models of Complex Systems", Russian Electrical Engineering, 2011, Vol. 82, No.11., pp.623-627. doi: 10.3103/S1068371211110125.

- [13] Lev V. Utkin, and Igor O. Kozine, "Stress-strength reliability models under incomplete information@, International Journal of General Systems, 2002, 31:6, 549-568, DOI: 10.1080/0308107021000061885

- [14] N.A.J. Hastings, "Physical Asset Management", 2015. doi: 10.1007/978-3-319-14777-2\_3

- [15] A. B. Petrochenkov, S. V. Bochkarev, A. V. Romodin, D. K. Eltyshev, "The Planning Operation Process of Electrotechnical Equipment Using the Markov Process", Russian Electrical Engineering, 2011, Vol. 82, No.11., pp.592-595. doi: 10.3103/S1068371211110113.

- [16] A. B. Petrochenkov, "On the Problem of Development of Models of Processing Operations Performed during Repair of Electrical Engineering Complex Components", Russian Electrical Engineering, 2013, Vol. 84, No. 11, pp. 613–616. doi: 10.3103/S1068371213110096.

- [17] E.V. Cota, L. Gullo, R. Mujal, "Applying Design for Reliability to increase reliability confidence", Proc. of Annual Reliability and Maintainability Symposium, 2014, art. no. 6798454, doi: 10.1109/RAMS.2014.6798454

# Conceptual Foundations of Modelling of Innovative Production Projects

Leonid Mylnikov

Perm National Research Polytechnic University - Electrotechnical Department

Komsomolsky Ave. 29, 614990, Perm, Russia

E-mail: leonid@pstu.ru

Abstract—At the moment there is a lack of methodological approaches to formalization of management of innovative projects relating to production systems, as well as to adaptation and practical use of the existing approaches. This article is about one potential approach to the management of innovative projects, which makes the building of innovative process models possible based on objective approach. It outlines the frameworks for the building of innovative project models, and describes the method of transition from conceptual modelling to innovative project management. In this case, the model alone and together with parameters used for evaluation of the project may be unique and depends on the special features of the project, preferences of decision-making person, and production and economic system in which it is to be implemented. Unlike existing approaches, this concept does not place any restrictions on types of models and makes it possible to take into account the specificities of economic and production systems. Principles embodied in the model allow its usage as a basis for simulation model to be used in one of specialized simulation systems, as well as for information system providing information support of decision-making process in production and economic systems both newly developed by the company (enterprise) and designed on the basis of available information systems that interact through the exchange of data. In addition, this article shows that the development of conceptual foundations of innovative project management in the economic and production systems is inseparable from the development of the theory of industrial control systems, and their comprehensive study may be reduced to a set of elements represented as certain algorithms, models and evaluations. Thus, the study of innovative process may be conducted in both directions: from general to particular, and vice versa.

Keywords: innovative project, management, decision-making, algorithm, analysis, concept, search for optimal solution innovative project, management, decision-making, algorithm, analysis, concept, search for optimal solution.

#### I. INTRODUCTION

The existence of fresh results that can be used in the products has become a resource which gives strategic advantages. However, it is essential to use such resource properly.

In large production systems time and budget for implementing any changes are strictly limited. Each of these projects requires key competencies some of which a company may not have. In such a situation, execution of the project gives the company new competencies and skills, as well as new impetus for its development.

Effect of innovations may take the form of improved consumer properties and higher level of standardization and automation of production, which in turn leads to reduced costs

High rates of economic growth become an additional factor under a free market economy. According to data from the Federal State Statistics Service in the period from 2009 to 2013, the product output in the Russian Federation (in million rubles) grew by 181,92%; and the output of innovative products grew by 350% which demonstrates economic expediency of innovative products.

System manufacturing innovative products had to be in a process of transformation manifested as the need to increase the number of product modifications, relationship links with other enterprises, and proprietary sub-systems as compared to traditional products. This makes higher demands for quick administrative decisions and high-quality innovation management, therefore the quality of management, as a rule, becomes a critical factor in the success of projects aimed at development and manufacture of innovative products and technologies, and addressing the problem of efficient management of innovative projects becomes more and more important.

Theory and practice of the management were developed through addressing local problems because it was hard to manage innovation as a single system [15] which created a lack of methodological approaches to formalization [formal characterization] of the management of innovative projects as a single system.

Because of this, while noting all benefits of holistic consideration of the problem of innovative project management, modern publications do not describe any models of innovative projects as complicated systems, which allows no effective solution of the issues of management, expertise and rationale. Such issues are often viewed as separate not interconnected challenges rather than a single process [12][15].

There are some special approaches to certain types of innovations. They depend largely on the sector of economy and sphere they are related to (organizational innovations, innovations in the field of service, technological innovations, innovations applicable to the products which affect their consumer properties, etc.).

Methods of solving management tasks and decision making used in product innovative projects are based on analysis of the project properties. Scientific and technical literature relating to innovative programs and processes contains description of several stages and functions of manager at each stage. A common feature is that all his decisions must be informed and reasoned [11].

The rationale needs the use of model. The way and method of modelling must solve the problem of increasing the efficiency of administrative decisions.

A model allows the manager to rule out the prospect that only some of available methods were used during project execution, determine the dynamics of its progress and set its parameters reasoning from the current and desirable dynamics.

#### II MODELLING OF INNOVATIVE PROJECTS

Development of methods of mathematic formalization of innovative project management has been reflected in several approaches.

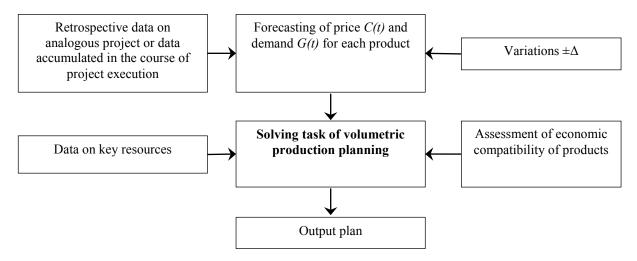

In the context of this approach volumetric production planning and procurement (acquisition) planning are the most studied. The principal research in this area focuses on support of administrative decisions in nonlinear-cost or combined-structure systems, and most studies focuses on cost minimization and demand forecasting. Only little research deals with training and promotion of decisionmaking skills with due regard for requirements of production systems [10]. Important problem arising from the above challenges is concurrent consideration of challenges of pricing (price formation), volumetric production planning and procurement planning. Solving of this problem raises the issues of market selection and internal structural organization of economic and production systems, and is defined "Wagner-Whitin's problem" [9].

Formalization of concurrent consideration of challenges (tasks) relating to market selection and volumetric production planning was first mentioned in [1], and continued to be a challenge. It has been shown that this is a NP-full task, and can be tackled only when certain factors are determined [10].

The perception of single innovations as constants is a very rough assumption. In 1995 Peppal suggested the use of game theory [8] in description of duplicating and improving innovations so that to take account of interaction and reciprocal influence between projects. This approach has generated new developments related to the issues of change management. Its promotion in the field of innovation management is currently connected with agent-based modelling and the use of forecasts. In early 2000s this approach was furthered by object-oriented modelling, and, when applied to economic and production systems, is known as multi-agent systems [4] taking into account such factors as independence, exposure to external shocks (influences), flexibility, pro-activities, and availability of intellectual control [3][7]. The most complex issue is to coordinate interaction between different parts of economic and production system [5].

Another approach is management model oriented at such event as innovation diffusion (Eric von Hippel) [1], namely, adoption and study of best practices of similar product manufacturing used in various production systems in an effort to find common features. This approach helps to

uncover common features and to provide guidance based on the same type of products and similar production systems.

Approach to innovation management in production systems is often based on some pattern of events that make up the process concerned (Jordan's modelling, Hein's logical modelling), through it does not take into account the relationship between different sub-systems and their interference.

Present-day development of methods of statistics-based management is establishment of databases of actual status of process, event and object. This approach presupposes that all facts within the framework of innovative process paradigm are true, and involves the use of interdependent and agreed databases, their relationship and processing rules [13]. This method may serve as a good base for designing information infrastructures in systems with well-established processes, but is not efficient for creating information infrastructures in dynamic systems, that is, introduction of innovations (novelties) entails a lot of changes in production systems.

There is a great number of practically developed methods and techniques of formalizing individual solutions that can be used in different special cases irrespective of management levels and types of innovation.

By knowing the peculiarities of innovative project to be executed, and the relevant economic and production system (its identification), one can reduce the modelling of its management to application of a number of standard or author's models and methods to each component of innovative project. This approach is justified by the high level of some challenges. So it would be reasonable to give due consideration for the decisive results which can be received from solving local tasks, especially in connection with the fact that evolution of technical and economic systems becomes more complicated both in number of elements and quality of their relations, and hence structuring of models allows changes of this type to be easily incorporated [17].

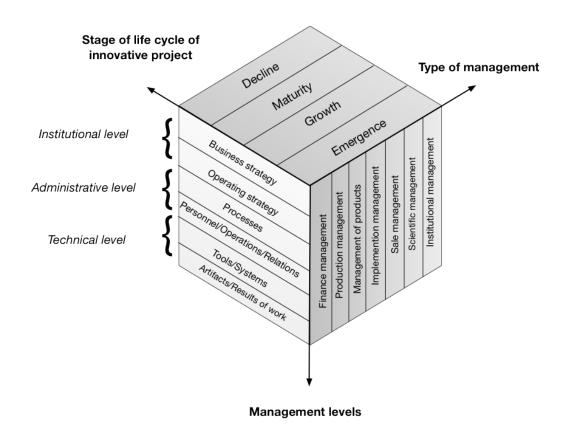

The challenge of choosing right methods and models to be used can be addressed by a decision-making person. To simplify the process, existing and known methods can be presented in a convenient form based on classification characteristics of innovative projects (refer to Fig. 1).

The application of this scheme is only to choose the classification characteristics<sup>2</sup> as shown in Fig. 1 [2]. In this case, to present methods and models means to indentify their location by reference to the chosen characteristics.

The next challenge is to combine them in an effort to make general assessments at decision-making points. Thus, it is essential to establish relationship between methods when they are combined.

On the one hand, interrelation of methods will depend on interrelation of sub-systems, their elements and tasks they help to address (structural scheme of economic and production system, sequence of management tasks to be solved, etc.). On the other hand, successive (application of some methods to determine internal parameters of others) or parallel (general assessments) application of some methods can be used to determine coefficients of others.

<sup>&</sup>lt;sup>1</sup> For instance, Jean Tirole has successfully addressed the issue of management in sector markets.

<sup>&</sup>lt;sup>2</sup> Only characteristics having common angles (Fig. 2) may be chosen.

If there are known structural interrelations a model of innovative project (innovative process) introduction can be presented as a matrix [16]:

$[M] = \left( [A][K]^T \begin{bmatrix} M_1 \\ \cdots \\ M_1 \end{bmatrix} \right),$

where

[A]- incidence matrix (demonstrates interrelations between sub-systems, methods and project parameters);

[M] - vector of summative assessments for each methods employed;

[K] - diagonal matrix of corrective coefficients;

$M_{i}$  – assessment of method employed;

I - number of combined methods employed.

Fig. 1. The Way of Combining Management Presentations to Choose the Right Methods and Techniques Suitable for Assessment of Outcome of Administrative Influences in Execution of Project

For the purpose of addressing economic challenges, results enabling to take optimal or admissible decisions are particularly important. Thus, there is the need for generic criterion which can be obtained by adding or deducting assessments made with the methods described herein [16].

In other cases, method interrelation can also be represented through adding, deducting, multiplying and dividing assessments obtained with these methods.

Thus, implementation of this approach reduces the modelling to a number of operations with mathematical descriptions of methods, techniques and models relating to certain tasks.

In this regard, it could be concluded that implementation of innovations and manufacturing of innovative products have "nucleus" - "generic production function" in the form of non-linear multi-factor dependence between output figures and vector of generic production factors.

## III. FUNCTIONAL APPROACH TO ADMINISTRATIVE DECISION MAKING IN THE EXECUTION OF INNOVATIVE PROJECT

The modelling theory outlines a few tasks that can be addressed with the use of models depending on the unknown. If we look at a model of innovative project implementation, we can highlight two objectives:

- 1) to establish internal setpoint of project parameters aimed at ensuring the achievement of given targets (goals) of the projects;

- 2) to determine production parameter values (settings) at the decision-making points.

If we look at examples of formalized objectives, then in the first case production function will dictate general criterial function as follows (refer to more detailed information [16]):

$$\sum_{j=1}^{l_1} u_j k_j (h_j - M_j)^2 + \sum_{j=l_1+1}^{l_2} u_j k_j M_j - \sum_{j=l_2+1}^{l} u_j k_j M_j \rightarrow min$$

where

h; - desirable value;

$k_{jj}$  - elements of vector of corrective coefficients **[K]** which, in turn, is calculated by the above formula:

$$k_j = \frac{k_{ij} - k_{iij}}{k},$$

where

$k_{BJ}$  - upper edge of the range of parameter variations in *j*-method;

$k_{HJ}$  - lower edge of the range of parameter variations in *j*-method):

$\mathbf{u}_{j}$  - assessment of importance of chosen methods (can be made with the use of both expert approach and assessment methods);

$l_1$ ,  $l_2$  - boundaries of groups depending on the criterial function ( $l \ge l_2 \ge l_1$ ),

$M_{\tilde{i}}$  - summative assessment of each method employed.

Search for optimal solution may restrict the targets of methods employed  $m_{ij}$  (components of summative assessments of methods  $M_i$ ):

$$m_{ij} \in G_{ij}; j = \overline{1,l}; i = \overline{1,n_l},$$

where

$G_{ij}$  – multitude of alternative parameter values (settings) for j – method;

i - parameter.

This objective can be reduced to a class of discrete multiparameter optimization tasks with certain restrictions, and achieved by using Bellman-Ford algorithm which is adapted method of dynamic programming for graphs.

As an example of second-type formalization, we will consider a volumetric scheduling task based on discrete volumetric production targets.

$$\begin{split} &\sum_{i} \sum_{h} K_{ih} \sum_{t} (C_h(t) x_h(t) + C_h(t) x_h(t)) \rightarrow max \\ &\sum_{i} \sum_{t} R_{ij} x_i(t) \leq P_j(t), \ j = \overline{1, M} \\ &\sum_{i} \sum_{t} S_{ki} x_i(t) \leq T_k(t), \ k = \overline{1, K} \\ &\sum_{i} \sum_{t} \alpha_i^q x_i(t) \leq G^q(t), \ k = \overline{1, Q} \end{split}$$

$$\begin{split} & \sum_{h} \sum_{t} R_{hj} x_h(t) \leq P_j(t), \ j = \overline{1, M} \\ & \sum_{h} \sum_{t} S_{kh} x_h(t) \leq T_k(t), \ k = \overline{1, K} \\ & \sum_{h} \sum_{t} \alpha_h^q x_h(t) \leq G^q(t), \ k = \overline{1, Q} \end{split}$$

where

$\mathbf{x}_i$ ,  $i = \overline{\mathbf{1}_{*}N}$  – vector unknown;

i type,  $C_i$ ,  $i = \overline{1}_* \overline{N}$  - net revenue from production of i - goods (estimated);

$R_{ij}$ ,  $j = \overline{1}_* M$ ,  $i = \overline{1}_* M$  - required capacity of each type of equipment per finished product;

$P_{j}$ ,  $j = \overline{1 \cdot M}$  - total capacity resources for each type of equipment in terms of average production rate of all equipment of that type;

$S_{ki}$ ,  $k = \overline{1, K}$ ,  $i = \overline{1, N}$  - required volume of key materials per finished product;

$T_k$ ,  $k = \overline{1, K}$  - volume of available key materials based on inventory in stock and procurement plan;

$$\alpha_i^q = \begin{cases} 1 - \text{if } i - \text{goods belong to } q \text{ category} \\ 0 - \text{if } i - \text{goods does not belong } q \text{ category} \end{cases}$$

$G^{q}$ ,  $q = \overline{1,Q}$  - restriction on sales market (marketing area) (estimated);

**K**<sub>ih</sub> - coefficient of correspondence between it and h goods, which shows economic feasibility of joint manufacturing of goods or group of goods within one production (as evaluated by one of methods of Slope One group on the basis of sales statistic data).

The use of forecasts in second-type tasks, even if they are very adequate, may result in variations (especially if there are crisis phenomena in the economy). If we include accidental variations in our model, we will get Markovsky process, which requires further research on the basis repeated modelling and statistic data – refer to Fig 2.

Thus, the designed models and production functions can be considered, as a set of "black boxes" of a sort, each with the relevant functional description [18]. This approach was first proposed by an American economist J.B. Clark.

In addition to the above models which take into account production functions, there are many models of certain units (production department, warehouse, etc.); models of types of activities (production, sales); and models of personnel, product, finance and other models.

Fig. 2. Hierarchy of Selection of school based on analytical hierarchy process [6].

#### IV. CONCLUSION

Based on the above, we can conclude that at present there is no uniform concept of project management that would allow us to perform focused search for administrative decisions instead of their analysis and sorting out. Development of conceptual business tends to focus either on separate management sub-systems (such as enterprise management information system [14]) or on separate subtasks (such as management of warehouse, sales, deliveries, etc. [18]).

Thus, development of the conceptual foundations of the theory of innovative project management is as topic as ever. It is precisely the understanding of conceptual foundations that facilitates the use of methods and approaches in this field of study as a tool of practical task solving.

It is shown, that development of conceptual foundations of management of product innovative projects is inseparable from development of theory of production system management. Their comprehensive study can be reduced to a number of elements embodied with specific algorithms, models and assessments, which makes it possible not only to take administrative decisions, but to design information system to manage economic and production systems as well.

#### REFERENCES

- F. Gault, E von Hippel, "The Prevalence of User Innovation and free Innovation Transfers," Implications for Statistical Indicators and Innovation Policy.MIT Sloan School of Management Working Paper #4722-09, January, Cambridge, MA, 2009.

- [2] M. Gepp, M. Amberg, T. Schaeffler, S. Horn, J. Vollmar, "Framework and rationale for economic considerations in industrial plant business," Systems Conference (SysCon), IEEE International, 2013.- pp 14 – 19.

- [3] V. Dignum, "An overview of agents in knowledge management," Heidelberg: Springer. 2006.

- [4] N. Jennings, "On agent-based software engineering," Artificial Intelligence, 117 (2), 2000, pp. 277-296.

- [5] T. Kaihara, S. Fujii, "Game theoretic enterprise management in industrial collaborative networks with multi-agent systems," International journal of production research. 46 (1). 2008. pp. 1297-1313

- [6] M. Lang, S. Kammerer, M. Amberg, "Projektportfoliomanagement in der IT: Priorisierung, Investition, Steuerung," Düsseldorf: Symposion, 2012. p. 442.

- [7] J. H. Lee, C. O. Kim, "Multi-agent systems applications in manufacturing systems and supply chain management: a review

- paper, "International Journal of Production research, 46(1). 2008, pp.233-265.

- [8] L. Pepall, "Imitative Competition and Product Innovation in a Dupoly Model," Economica. №64, 1995. pp. 265-269.

- [9] H. M. Wagner, T. M. Whitin, "Dynamic version of the economic lot size model," Management Science. 5. 1958. pp. 89-96.

- [10] W. V. den Heuvel, E. Kundakcioglu, J. Geunes, E. Romeijn, T. C. Sharkey, A. P. M. Wagelmans, "Integrated market selection and production planning: complexity and solution approaches," Mathematical Programming, Volume 134, Issue 2, 2012, pp. 395-424.

- [11] P. Young, "The evolution of conventions," Econometrica № 61, 1993. pp. 57-84.

- [12] V. Vinokur, A. V. Trusov, "Intelectual properties as basis of innovation activities," Perm: PSTU Publ., 2004. – 271 p. (In Russian)

- [13] T. Gavrilova, V. Khoroshevskiy, "Knowledge bases of intelligent systems,". SPb: Piter Publ., 2000. – 382 p. (In Russian)

- [14] Y. Zelenkov, "Methodology of strategic management of inforantion system development for huge industrial enterprise in modern conditions," Dr. tech. sci. autor. diss. Chelybinsk. 2013.-42 p. (In Russian)

- [15] L. Mylnikov, "Microeconomic problems of innovation project management," Management problems, 2011. №3, pp. 2-11. (In Russian)

- [16] L. Mylnikov, "Management of innovation projects based on an integral criteria," Management of big systems. Issue. Moscow: IPU RAS Publ., 2010, pp. 128-151. (In Russian)

- [17] L. Mylnikov, A. Trusov, N. Khoroshev, "Review of concepts for information management of innovation projects," Information resources of Russia, 2010. No.3, pp.34-39. (In Russian)

[18] V. Shiriaev, E. Shiriaev, "Management of business process," –

- Moscow: Finansy I Kredit Publ.; INFRA-M Publ., 2009. 464 p. (In Russian).

# City Outdoor Lighting System Control. Problems and Prospects

#### Andrei Bachurin

Perm National Research Polytechnic University – Electrotechnical Department Komsomolsky Ave, 29, 614990, Perm, Russia

E-mail: bachurin@ellips.ru

Abstract—This review describes current problems, trends and prospects of the quasi-automatic light control system. The lighting systems of million cities.

*Keywords*: control system, lighting system, management problems, prospects for control systems, control in lighting trends.

#### I. OBJECT OF STUDY

#### a. Cities

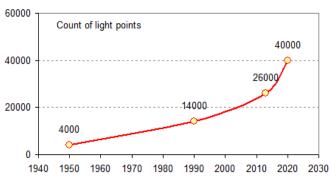

The objects of study are the largest cities in Russia: Ekaterinburg, Kazan, Perm. These cities are administrative, industrial and cultural centers of large areas and they have developed network of outdoor lighting (Table 1).

TABLE I

MAIN CHARACTERISTICS OF CITIES

| City         | Square,<br>sq.km. | Official number of residents | Official number of light points |  |  |

|--------------|-------------------|------------------------------|---------------------------------|--|--|

| Perm         | 800               | 1026000                      | 29000                           |  |  |

| Ekaterinburg | 468               | 1428000                      | 41000                           |  |  |

| Kazan        | 614               | 1206000                      | 65000                           |  |  |

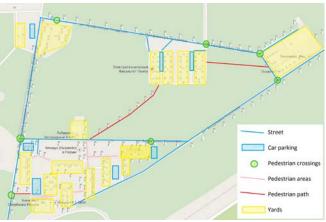

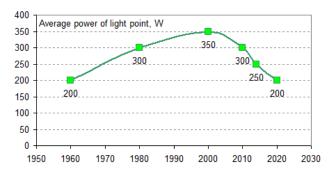

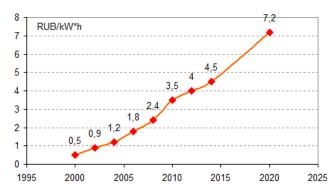

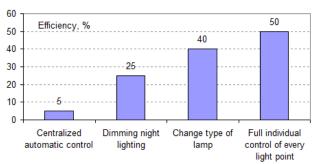

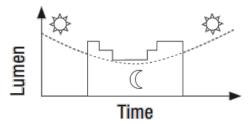

Cities are characterized by a large area, considerable extent in latitude and large difference in weather conditions at one and the same time (Fig. 1).

Fig. 1. Perm city from satellite photo.

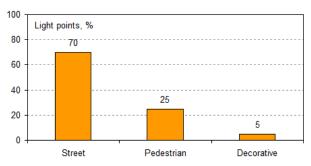

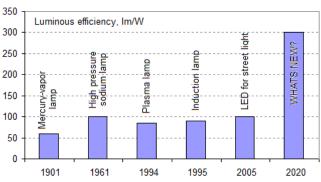

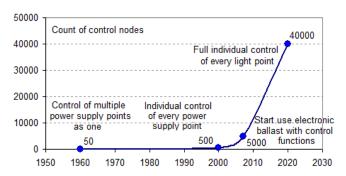

Lighting systems of these cities are characterized by the presence of all types of lamps (Fig. 5), different types of lighting control systems, illuminated objects of all possible types (Table 2) and modes (Table 3) of illumination, a single

lighting control center, a small number of service personnel, high demands on energy-efficient lighting.

#### b. Classification of illuminated objects

Street lighting can be divided by illuminated objects into 3 main categories and some subcategories (Table 2), each of them can be characterized by the following common features:

- Illumination is regulated by standards (STD);

- Illumination of the object is normalized (NORM);

- Illumination of the object can be changed depending on external conditions (VAR NORM);

- There is a standardized schedule of the object illumination (SHED);

- Schedule of the object illumination can be changed depending on external conditions (VAR SHED).

TABLE II CATEGORIES AND OBJECTS

| Category   | Object               | STD | NORM | VAR | SHED | VAR<br>SHED |

|------------|----------------------|-----|------|-----|------|-------------|

|            | Highways             | *   | *    | *   | *    | *           |

|            | Streets              | *   | *    | *   | *    | *           |

|            | Car parking          | -   | -    | *   | *    | *           |

| Street     | Tunnels              | *   | *    | -   | *    | -           |

| lighting   | Road signs           | -   | -    | -   | -    | *           |

|            | Road markings        | -   | -    | -   | -    | *           |

|            | Pedestrian crossings | *   | *    | -   | -    | *           |

|            | Crossroads           | *   | *    | -   | -    | *           |

|            | Pedestrian areas     | *   | *    | *   | *    | *           |

| Pedestrian | Yards                | *   | *    | *   | *    | *           |

| lighting   | Pedestrian paths     | *   | *    | *   | *    | *           |

|            | Athletic facilities  | *   | *    | -   | -    | *           |

|            | Parks and gardens    | -   | -    | *   | *    | *           |

| Decorative | Architectural        | -   | -    | *   | *    | *           |

|            | lighting             |     |      |     |      |             |

| lighting   | Outdoor advertising  | -   | -    | *   | *    | *           |

|            | House numbers        | -   | -    | *   | *    | *           |

It should be noted that the existing standards for most objects are very flexible and lack of base building nouns and other standards concerning lighting of there is a certain objects [5][6].

Lamps of different categories are located near each other and have to work synchronously. Ideally, the lamps must insure each other in case of failure.

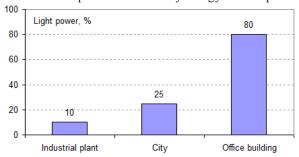

The approximate ratio of the objects in city lighting categories is shown on Figure 2.

Fig. 2. The ratio of the urban lighting categories.

Objects (categories) can be grouped by lighting modes (Table 3) [5][6].

TABLE III

TYPICAL LIGHTING MODES OF OBJECTS

| 1 YPICAL LIGHTING MODES OF OBJECTS                          |                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Objects                                                     | Lighting mode                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Highways,<br>Streets,<br>Pedestrian<br>areas                | The lights are switched on and off according to the schedule with adjustment for the current value of illumination, at night by low traffic density, the luminous flux can be reduced by 30% while decreasing traffic to 33% and by 50% while decreasing traffic to 20%. Depending on the object, there are different rates of light and illumination should not be reduced at least 4 lux. |  |  |  |  |  |  |

| Road<br>markings,<br>Pedestrian<br>crossings,<br>Crossroads | Lighting should switch on and off simultaneously with the appropriate lighting of streets, but the change of the luminous flux at night is not allowed.                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| Tunnels,<br>Road signs                                      | Lighting should work around the clock without changing the luminous flux.                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

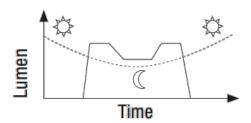

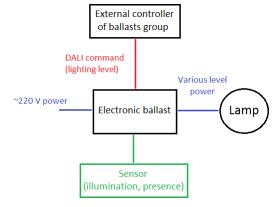

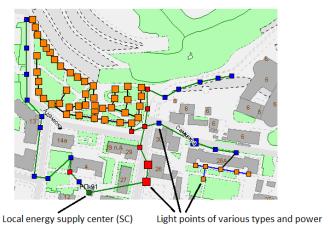

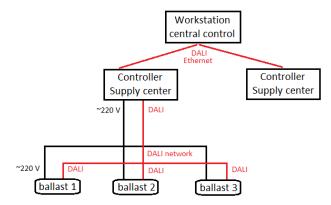

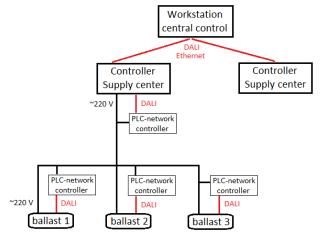

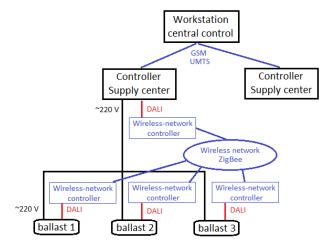

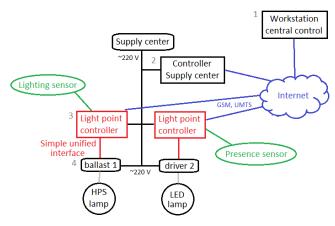

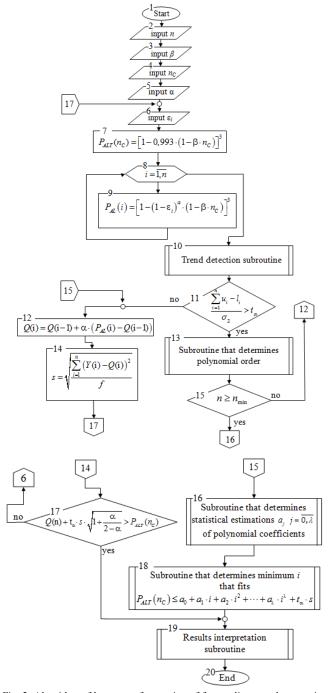

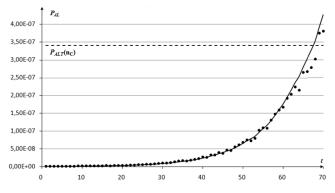

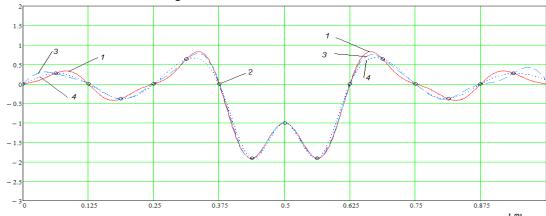

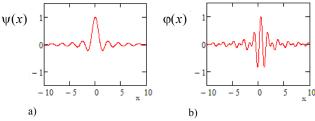

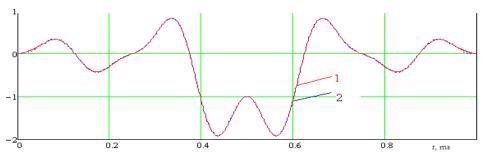

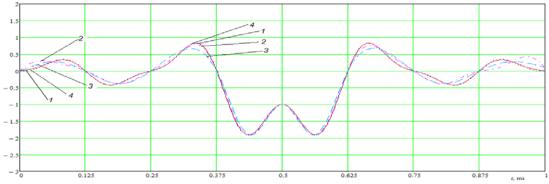

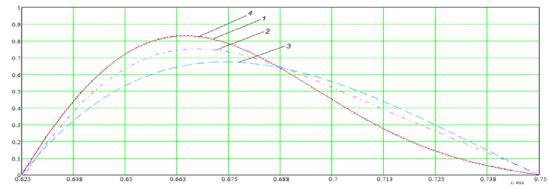

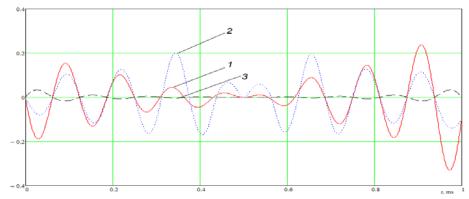

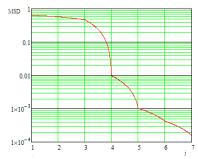

| Pedestrian<br>paths, Car<br>parking                         | Lighting should switch on selectively (some light points), if it is necessary, according to presence and light sensors data.                                                                                                                                                                                                                                                                |  |  |  |  |  |  |